MIT-LL 90nm Test Chip

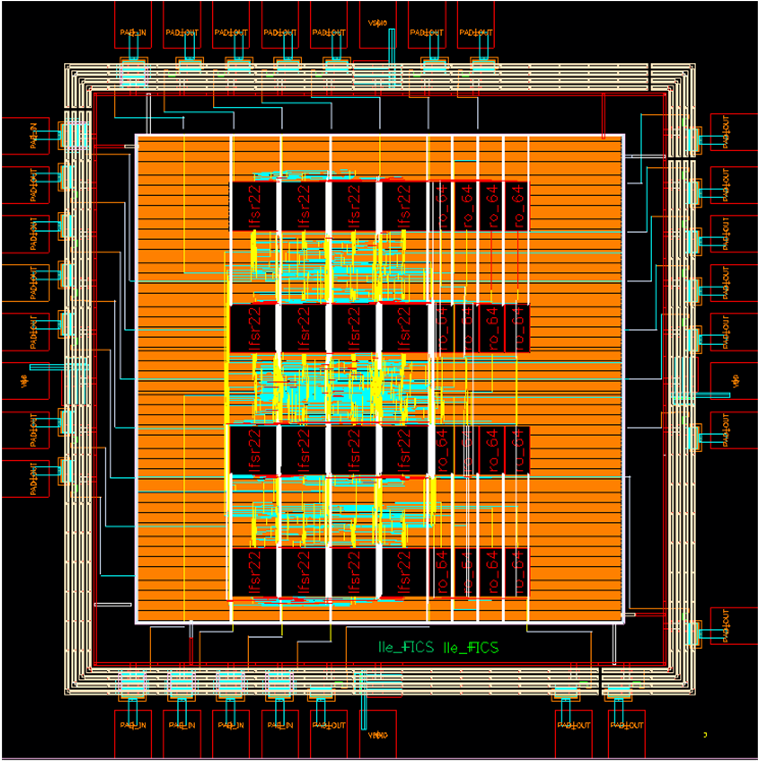

The effectiveness of a physical obfuscation method depends on how effectively it can go through all the different steps of integrated circuit design and development from RTL to GDSII and fabrication. With that in mind, as shown in the figure, we implemented the “LLE - Last Level Edit” in a set of benchmark circuits consisting of ring-oscillators, linear feedback shift registers (LFSR), and S38417 from ISCAS’89 benchmark circuits. To design, implement, verify, and fabricate the LLE integrated benchmark, we utilized Cadence Genus, Cadence Innovus, Calibre DesignRev, Cadence Virtuoso, and Cadence Tempus electronic design automation (EDA) tools with 90nm MITLL Low-Power FDSOI CMOS Process.

Left side shows te final GDSII of LLE Test chip and right shows the fabricated chip.