Secure and Reliable AI in Chip Design

Security and Optimization for cloud-EDA Platform

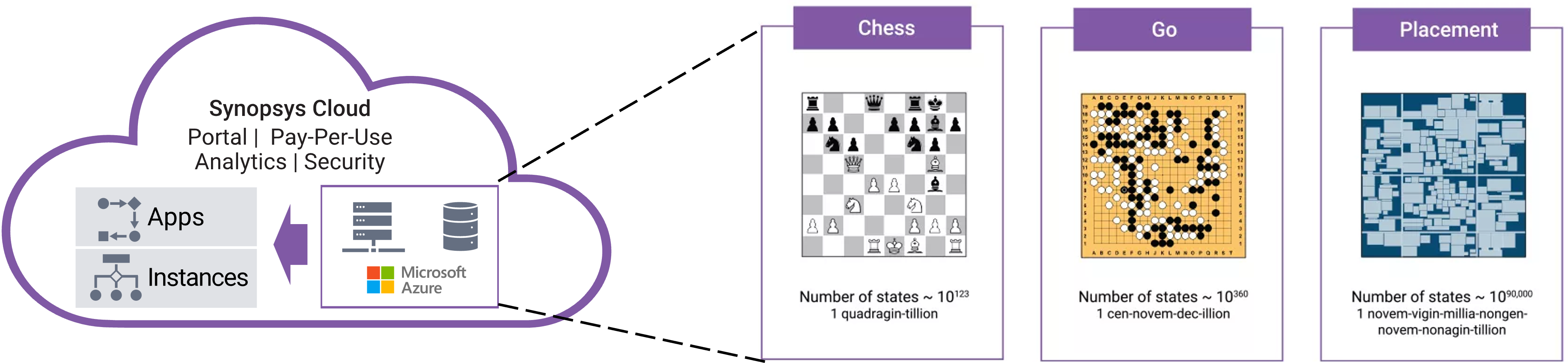

Traditionally EDA tools used for IC design, are installed in local machine. However, cloud-based EDA tools are taking that place now. IC design is an extremely complicated process. For example, a typical placement step considers 10^250 times more possibilities than a go/chess game. AI is empowering these steps to reduce the search space. Moreover, the sensitive design data and processing in cloud require more comprehensive protection than before. Hence, AI-chip design refers to the integration of artificial intelligence (AI) techniques in the various stages of the chip design process to enhance efficiency, fast convergence, and performance. This approach leverages machine learning algorithms, data analytics, and automation to streamline the complex and time-consuming tasks involved in designing integrated circuits. However, these AI-designed chips are exposed to various attacks - poisoning of the AI model, leaking of training dataset, and model extraction. Moreover, none of the existing AI-based chip design methods follow the manufacturing test and reliability guidelines. I plan to develop AI-assured chip design tool that leverages the industry standard during feature collection and leaves no trace for adversarial ML attacks.